| .cargo | ||

| .vscode | ||

| lds | ||

| src | ||

| .gitignore | ||

| 20240519-kernel_init_diagram.png | ||

| 20240520-kernel_init_diagram.png | ||

| build.rs | ||

| Cargo.lock | ||

| Cargo.toml | ||

| README.md | ||

| RESOURCES.md | ||

| created | modified |

|---|---|

| 2024-05-13T14:28:49-05:00 | 2024-05-19T17:41:01-05:00 |

kernel

A kernel for RISC-V written in Rust. Currently focused on running on QEMU generic riscv64, advice and assistance welcome & encouraged.

Progress

-

2024-05-19: As of right now, the basic "stuff" for initializing the kernel is there.

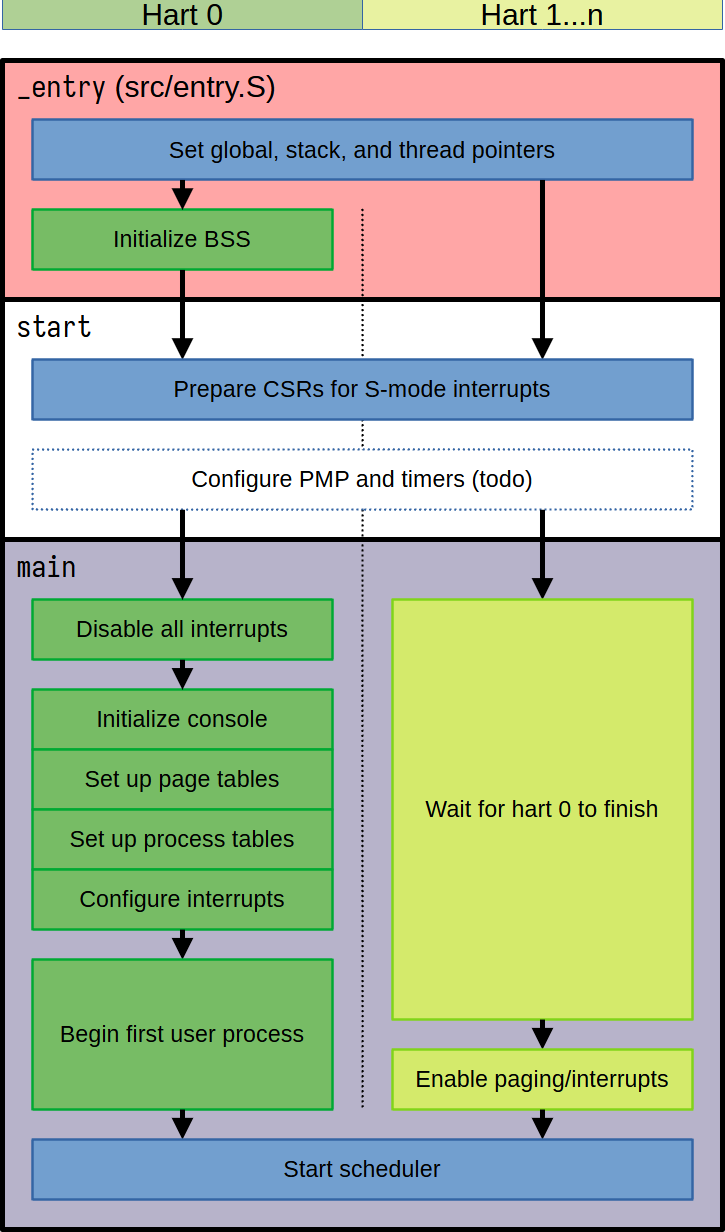

The diagram below shows what I'm thinking as far as what the init process should be. This is what I'm currently working on implementing, and I will update this chart (and prettify it) more -

2024-05-20: I added entry.S and entry_alt.S, its planned replacement, and rewrote some of the code. I also switched from using the

spinning_topcrate tospin, sincespinning_topdid not have out-of-the-box support for a one-time spinlock. Here is a new flowchart, replacing the previous one, showing what the kernel init process is:

Research and implement

- Basics

- Processes

- Virtual address spaces, page tables

- Files, directories

- Pipes

- Multitasking, time-slicing

- Syscalls

- CPU cache

- User authentication, login

- File protection, permissions

- Mountable file systems

- Paging to disk

- Sockets, network support

- Interprocess communication

- Device drivers

- User applications

Resources

See RESOURCES.md